因為真的非常迫切需要有一套完全支援 UML 2.x 的 tool 來畫圖,

去年開始就非常努力的到處找來找去,

雖然著名的 RSA (Rational Software Architect) 還不錯,

也很方便 run RUP (Rational Unified Process) 的流程,

但是它的 UML 2.x 支援度實在是太爛了...

最後找上了 Google 裡打廣告打最大的 Visual Paradigm 這家公司的產品 VP-UML。

這家雖然有提供免費的 Community Edition,

但是那在每個 project 只能開一張圖,

而且 export 出去的 image 還會打上滿滿的浮水印,

相當不利於用在正式場合上,

而且雖然號稱支援 UML 2.x 但其實功能還是有殘缺,

所以在這之前也很仔細的評估了其它軟體,

如 MagicDraw 和 Poseidon 等等,

但還是以 VP-UML 功能最齊...

仔細的讀完他們的版本比較表後,

覺得最適合我個人使用且價錢較合理的版本是 Modeler Edition,

於是就刷了 US$ 118.5 (US$ 99 是軟體本身的費用,另外加收 20% 的 1 年維護費),

這已經是去年的事情了...

基於這是花錢買的而且真的有用到,

但是有些關鍵功能還是有缺,

加上他們的客服人員在 forum 上回應得相當勤快,

只要有把問題反映上去幾乎都會出 patch 等等的因素,

這陣子開始決定要每隔一段時間嚴密的測試它的功能,

看能不能透過這種方式催生一套真正支援 UML 2.x 的 tool...

不過主要障礙還是在英文溝通上,

最近突然注意到 Visual Paradigm 是家香港公司,

說不定私下用中文寫 e-mail 對方看得懂?

如果真是這樣的話就能省下很多時間了。

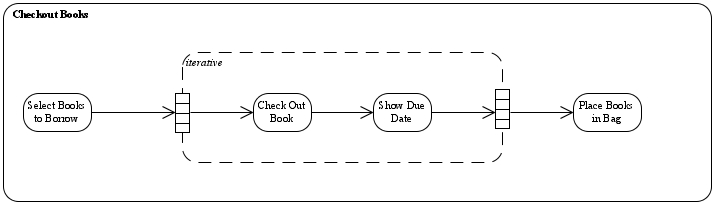

這次測試的是很多 UML tool 都不太注重的 Activity Diagram,

也許它被忽略的主要原因是與 code generation 無關,

所以沒有被很重視。

VP-UML 沒支援的圖大都是從 O'Reilly 的 UML 2.0 IN A NUTSHELL 英文版電子檔 cut 下來的,

等新買的 ScanMaker 5950 到手之後再來掃中文版的圖,

但這並不代表這篇的圖就一定會更新。

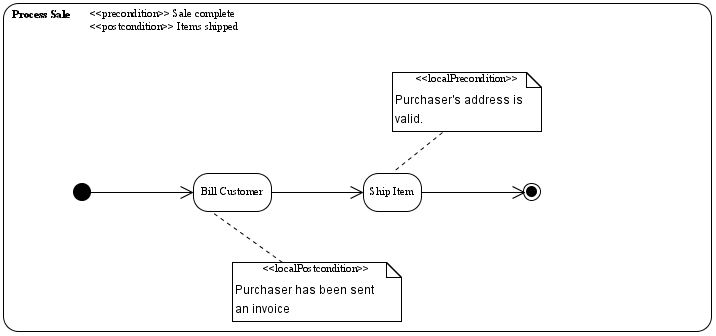

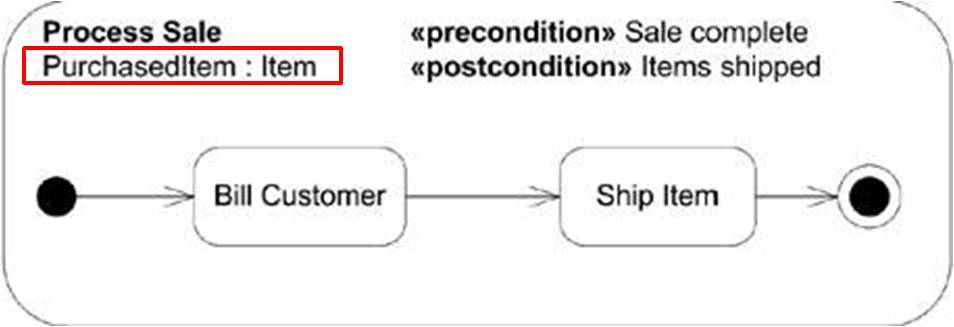

第一項測試:precondition/postcondition, localprecondition/localpostcondition, variables

在這項測試中就能順便發現一件事,

那就是 stereotype 是可以被任意新增到 note 上去的 (RSA 並沒有這項功能,一大敗筆),

VP-UML 已經為 note 預設了 localPrecondition 和 localPostcondition,

所以並不需要額外新增,

直接選下去就有了。

Activity 本身也有 precondition 和 postcondition 的欄位可以填寫,

只要有寫就會顯示出來,

這個設計相當不錯。

不過在這個測試中我也發現到 variable 雖然可以加入,

但並沒有提供任何方式將它顯示出來:

這是比較可惜的一點,

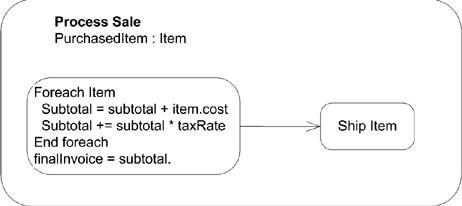

因為 UML 2.x 允許我們在 action 上直接填寫 algorithm:

這時是否能支援變數的顯示就相當重要了。

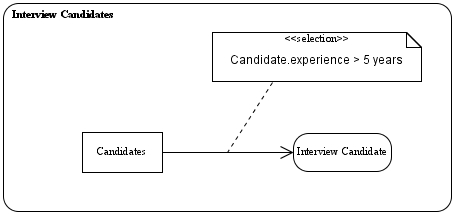

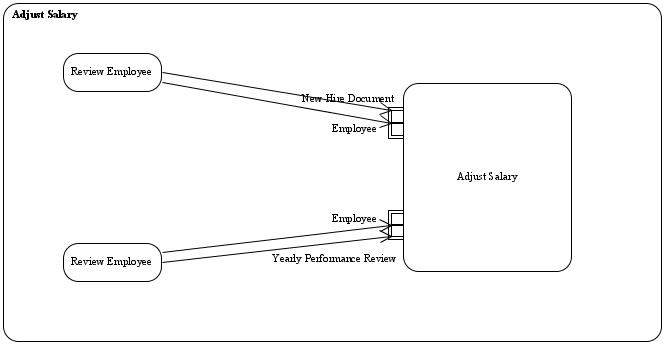

第二項測試:建立 Object Node

一定會有人覺得很奇怪為什麼要做這項測試,

這是因為 RSA 沒有辦法支援這項功能,

在 RSA 裡要不就是直接使用 intput/output pin,

要不就是得用有標上 centralbuffer 這個 stereotype 的 Object Node 代替,

這樣容易形成語意上的混亂並造成閱讀障礙;

在這裡可以看到 VP-UML 表現得相當好,

不過 note 的 default stereotypes 裡並沒有 selection 這項,

所以我自己加了上去。

第三項測試:Parameter Set

這個可以說是當今世上絕大多數 UML tool 的罩門,

也是我當時決定捨 MagicDraw 投靠 VP-UML 的原因之一,

支援 parameter set 的 tool 實在是太少了,

可見 VP-UML 的開發團隊在這方面有努力過,

美中不足的地方是操作介面並不十分親和。

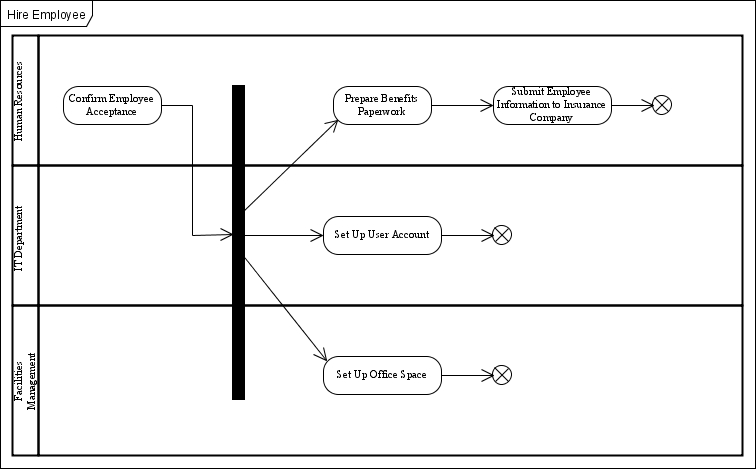

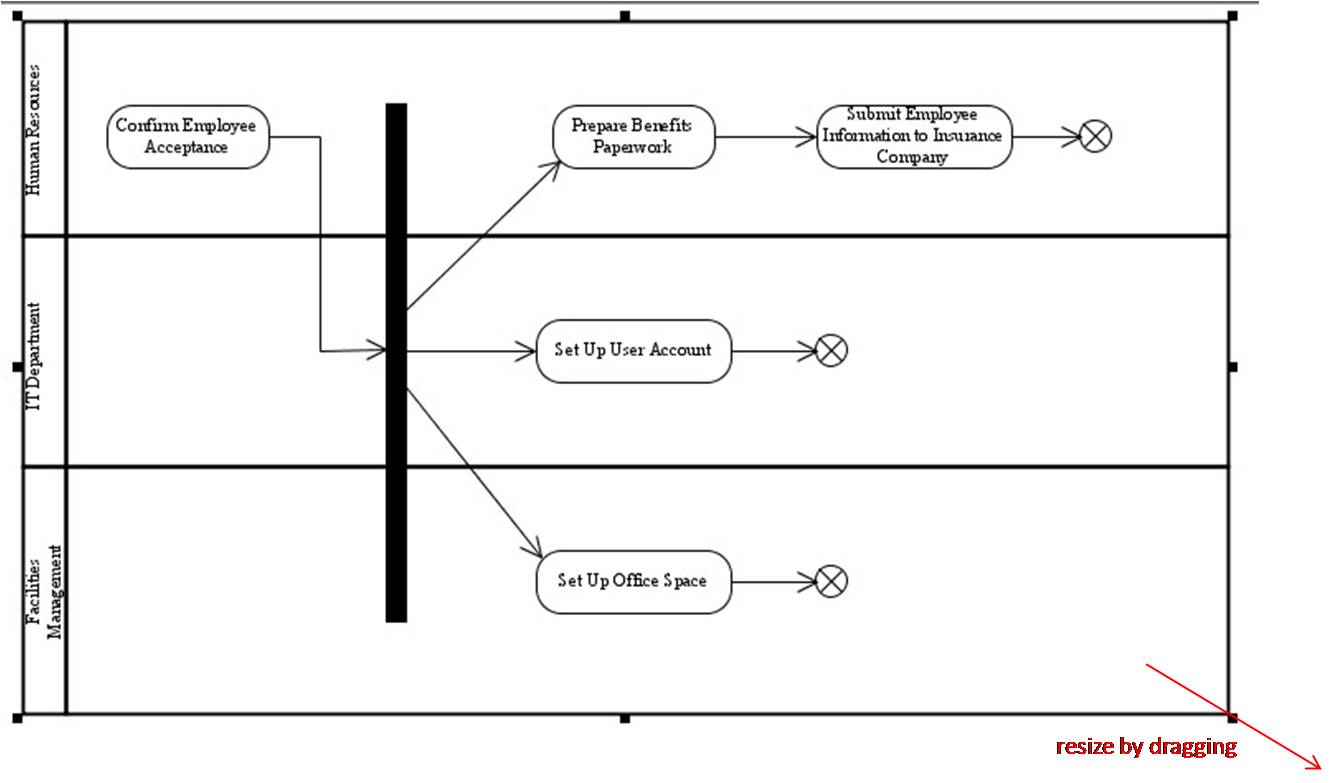

第四項測試:Acitivity Partition (Swimlane)

目前大部分的 UML tool 都有支援了 (RSA 6.x 在這方面有很多問題,7.x 已經修正),

VP-UML 在這方面的基本表現也還不錯,

不過對於 multi-line paritition name 的 alignment 支援並不完善 (稍後也會提到類似的缺陷),

譬如上圖中因為 Facilities Management 這個 name 分成兩行顯示,

其它兩個 parititions 的 name 就無法自動對齊中線 (也沒有設定可以這麼做);

此外 VP-UML 也不支援將 stereotype 顯示在 partition name 上方的功能:

也因為 paritition name 無法支援格式化輸入的功能,

若要表示一個 class instance 也沒辦法做出下劃底線的效果,

這點實在相當可惜。

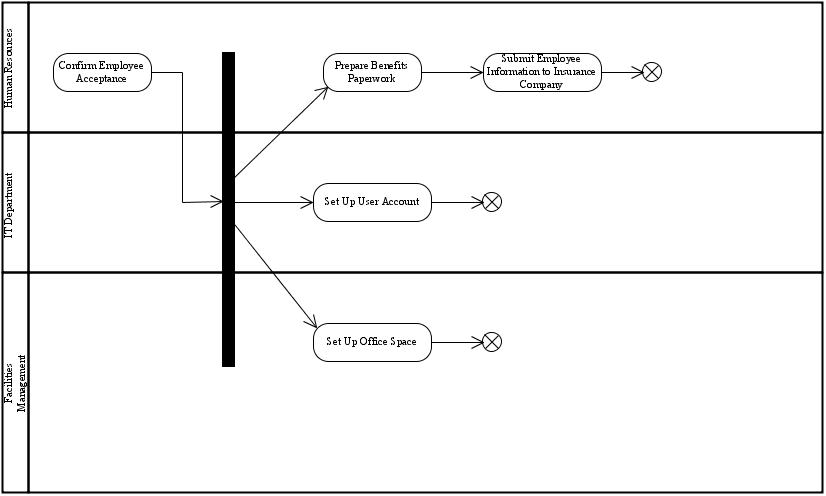

另外就是剛剛提到的 multi-line partition name 的問題,

其實這個問題可以 generalize 成 multi-line element name:

在上圖框起來的地方可以看到 Facilities 和 Management 之間有個奇怪的符號,

這是為了讓 Facilities Management 能顯示成兩行,

而在輸入時利用 ctrl-enter 強制斷行造成的,

所以那個奇怪的符號很可能是 newline character。

這個問題其實也會影響到第一項測試裡所提到的一個功能,

就是直接在 action 上面填 algorithm,

這樣搞下去那個 action name 在 model explorer 上肯定會變成一大串字,

而且換行的地方還會冒出上面的那種字元。

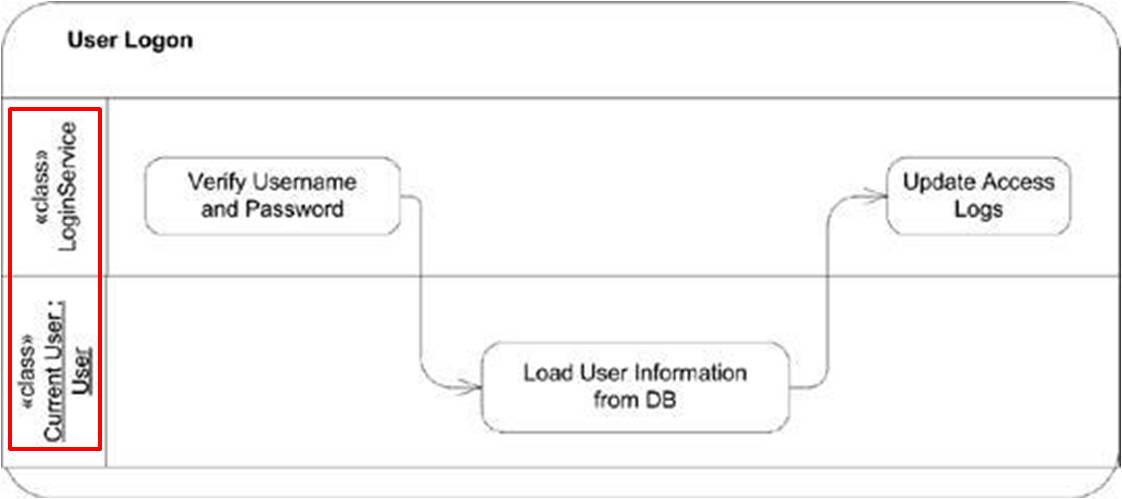

測試五:expansion region

這是在描述 foreach 之類的語意時很有用又簡潔的表示法,

目前只有極少的 UML tool 不支援,

大部分的 tool 都已經做得很不錯了,

要是有哪個團隊做出來的 tool 要是不支援它真的應該通通去撞牆;

VP-UML 在這方面表現得也相當不錯,

不然我也不可能會想花錢去買。

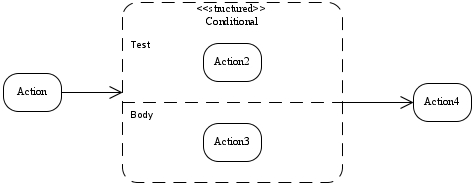

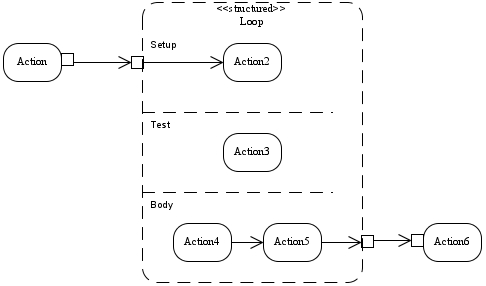

測試六:conditional node & loop node

這兩種表示法鮮少 UML tool 支援它們,

雖然 OMG spec 說可以在 structured activity node 分割成數個 region 來加以實現,

但並未詳細描述它們的圖形應該長怎樣,

變成 UML 2.x 規格裡的一大漏洞;

由於 MagicDraw 是以類似上圖的型式來支援的,

所以我在 forum 上表示希望 VP-UML 也這麼做,

他們也真的做出來了,

不過還有一些小 bug 存在,

像是 input pin 在 loop node 上時可以接受來自 loop node 內部 action 而來的 object flow,

以及 conditional node 上無法放置 input/output pin 的問題,

還有像是上圖的 loop node 偏右方的虛線莫名其妙被吃掉的問題等等;

但是不管怎樣,

有了這兩種表示法就能大幅簡化 activity diagram 的複雜度,

所以也是我相當重視的功能之一。

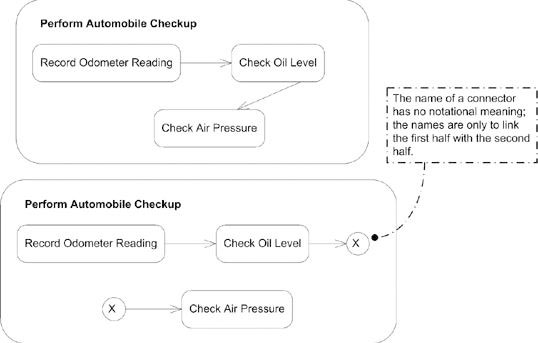

測試七:connector

不知道為什麼 VP-UML 並沒有支援 Connector,

如果需要將 Acitivity Diagram 貼在正式文獻上,

常常會因為版面限制等問題需要利用它來縮減圖的寬度,

否則要達到相同效果必須把 control/object flow 拉得錯綜複雜的,

使得版面混亂閱讀困難,

這個部分之後我會去 forum 上問問看是否有解。

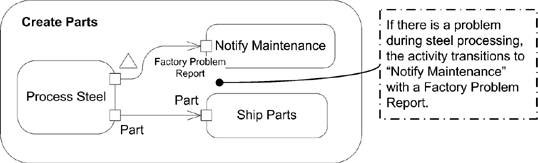

測試八:exception pin

這是個不太常見的表示法,

但是既然書上有就拿來測試測試,

很顯然 VP-UML 並沒有直接支援這種 pin,

去 forum 上問的話說不定他們會叫我直接去 common 面板拉個三角形來用?

測試九:input/output pin without in/out edge

這雖然是選擇性的表示法,

但是我覺得還蠻重要的,

因為如果一個 pin 沒有 in/out edge,

一般人根本無法分辨那個 pin 是 input pin 還是 output pin,

所以才需要在這種狀況下畫出箭頭來表示方向 (類似 value pin 那樣),

有時間的話可能要請他們新增一下這種表示法才行...

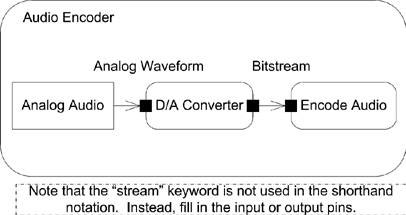

測試十:shorthand notation for streaming edges

這也是選擇性的標示方法,

直接把 pin 塗黑代表 action 對 input/output pin 的資料處理是採取 streaming 的方式,

有這項功能的話版面可以更加簡潔,

對做 multimedia 的人來說還蠻有用的;

VP-UML 並沒有支援它。

最後是要小小抱怨一下它的 partition resize 功能,

如果像下圖這樣將右下角的點往右下角拖曳來改變大小的話:

我相信很多人都是預期 resize 完後每個 partition 的相對高度還是不變,

但是結果卻十分出乎意料:

只有最下面的 paritition 變大了,

雖然我也知道要做到大家希望的那種結果是有點難度的,

不過還是希望能 user-friendly 一點...

另外就是沒有「平均分配高度」這種功能,

也是很不方便的地方之一。

以整體來說,

VP-UML 不管是在要錢或是不要錢的領域裡,

都算是對 UML 2.x 支援蠻完整的 tool 了,

之後還會想辦法抽出時間來寫其它 digrams 的測試,

如果有熱心人士能幫忙轉成英文把問題反映到他們 forum 上去是更好,

不然我每次都要花很多時間設法用英文把問題描述出來,

實在是有點累人...

VP-UML 預設的 Dialog 字型和 11pt 的字體大小,

不知道為什麼很容易形成鋸齒 (就算改成 Times New Roman 也沒有什麼改善),

其實圖形的邊也常出現鋸齒,

就美觀的角度來看其實缺陷還不小,

不過做工程的人就沒必要這麼講究了。